Parallel Computing CM30225

**Russell Bradford**

2023

CM30225

Parallel computing as a topic has been around for as long as computers have been around

But recently it has come back into fashion... for reasons to be explored in this Unit

You have PCs, laptops and phones that are multicore: multiple processors are in the mainstream

This Unit will look at hardware and software in the context of parallel computing

Structure of this unit: starting with 3 hours lectures per week

- Wednesday 10:15

- Thursday 10:15

- Friday 14:15

The aim is to cover the necessary material early in the semester which will leave the last few weeks free for revision and problems classes; and to lay the groundwork for the assignments

Usual combination of assessed coursework and exam: two pieces of coursework plus exam

- 1. Shared memory programming (15%)

- 2. Distributed memory programming (10%)

- 3. End of unit exam (75%)

Coursework timelines (subject to change):

- 1. set Thu 19 Oct due Wed 15 Nov

- 2. set Thu 16 Nov due Mon 8 Jan 2024

Feedback on coursework will be provided via Moodle. There will be general feedback that applies to many people and some individual feedback

Note that marking parallel programs is *very* time intensive (for reasons you will learn in thus unit!), so please don't expect a speedy turnaround

The coursework will be writing some parallel programs in C on a supercomputer

Though you **must** already be familiar with writing C, you may wish to brush up on your C in preparation

There is a "Remind Yourself About C" document on the Unit Web page

Week 6 (starting 6th Nov) will be a "consolidation week" No lectures for the whole of Computer Science (CM Units) Presumably other Departments will carry on as usual

**Aims** To give students the ability to recognise and understand the problems and opportunities afforded by parallel systems; to recognise the differing types of parallelism available and make advised choices between them; and to take advantage of progress in technology as modern computers become ever more parallel.

Learning Outcomes Students will be able to:

- 1. write and debug simple parallel programs;

- recognise the issues surrounding concurrent access to data;

- 3. describe the various kinds of parallel hardware, parallel programming methodologies and the relationship between them

Skills required:

- 1. Comfortable writing C

- 2. Ability to think through complicated situations

- Basics: supercomputers and the consequences of Moore's Law; bandwidth vs latency; speedup, efficiency, scalability; Amdahl's & Gustafson's Laws; Flynn's taxonomy, SPMD; distributed, shared, NUMA and other memory architectures.

- Shared memory computing: multicore systems (cache coherence and bottlenecks); mutual exclusion and critical regions; low level constructs including POSIX threads and synchronisation methods such as barriers, locks, semaphores, etc.; language-level support including monitors, OpenMP; vector and array (SIMD), HPF, Cn.

- 3. Distributed computing: clusters, message passing, MPI. Programming using MPI (and SLURM).

- 4. Parallel algorithms and data structures.

- Topics in Parallel Computing: examples might include HPC; MapReduce; distributed file systems; the Grid; GPGPU and OpenCL; instruction level parallelism (SWAR, VLIW).

## Here Be Dragons

Note that this is a Final Year Unit, so is a lot more stretching than previous years. It contains a lot of material as parallelism is a big subject

Also it is *very important* that you are a confident programmer with good experience in C. Otherwise you will be spending a disproportionate amount of time on the coursework. Do think very carefully about this

Many in the past have assumed "it will be ok, I can wing it", and subsequently had great difficulty in the coursework

The coursework is trivial as a sequential program, but very testing as a parallel program

## Unit Outline Resources

The subject of Parallel Computing is nearly as old as that of computers and so there are *lots* of books

None of them really suitable for this course, as we will try to take a broad overview of the subject

Part of the problem of parallel computing is that there is no simple unified model (like von Neumann for sequential computing), and everybody has their own idea on how things should be done

Leading to loads of books saying "this is the one true path to parallel computing"

Take them with a pinch of salt!

Some books I found on my shelf:

### Hardware

- "Highly Parallel Programming", Almasi & Gottlieb, Benjamin Cummings

- "Computer Architecture and Parallel Processing", Hwang & Briggs, McGraw-Hill

## Software

- "Concurrent Programming Principles and Practice", Andrews, Benjamin Cummings

- "Introduction to Parallel Computing", Kumar, Grama, Gupta, Karypis, Benjamin Cummings

- "Concurrent Programming", Burns & Davies, Addison-Wesley

- "Designing and Building Parallel Programs", Foster, Addison Wesley

- "Distributed Algorithms", Lynch, Morgan Kaufmann

## Unit Outline Resources

#### Theory

- "Principles of Concurrent and Distributed Programming", Ben-Ari, Prentice Hall

- "Communicating Sequential Processes", Hoare, Prentice Hall

N.B. Some of these were given to me by the publishers so I'm not saying they are the best books out there

The thing to do it look at several and find one that suits you: they contain roughly the same material

You don't need me to tell you that there is a large amount of material out there on the Web?

Wikipedia is fairly accurate in this area: but, as usual with Wikipedia, you should check with other sources

There is a Unit Moodle page, but as Moodle is so horrible I tend to use my own Web page:

http://people.bath.ac.uk/masrjb/CourseNotes/cm30225.html

Remember:

You are expected to do some work outside of lectures

Lectures are the *start* of the learning process, not the end!

These slides are reminders to me on what to say in lectures

They are often abbreviated in style, and so are not the whole story and would not be suitable to be quoted verbatim in an exam

Don't try to copy everything down from the slides in lectures—the slides will be available after each lecture

Instead, make a note of what is important and use that later—in conjunction with the slides—to guide your further reading and study

Do not rely purely on my notes for your revision

People who do this live to regret it

Like every Unit, you are expected to read around the subject for yourself

You need to take your own notes, read, and participate

You don't expect to get fit simply by paying to joining a gym...

"If you have college courses in CS, buy the books and spend day and night the few days before class going through the books and taking notes and answering questions and programming examples before the first class even starts. If you really want to do this in your life, that's what you should do, not just wait for the education to be handed you. Those who finish at the top will always be in high demand. You can learn outside of school too but you have to put a lot of time into it. It doesn't come easily. Small steps, each improving on the other, is what to expect, not instant understanding and expertise."

Steve Wozniak, co-founder of Apple

Computer Science is not a spectator sport

Anon

## Background

You have a problem you wish to solve faster. What do you do?

1. You think hard and devise a better solution

Clearly this is a stupid thing to do. Programmers are much too lazy to do this

2. You get a faster processor

Better. This used to work, but not any more: processors have pretty much levelled off at around the 3-5GHz mark and don't seem to be getting faster

3. You get a multicore machine and run the problem in parallel

This *must* be the solution!

Isn't it?

One purpose of this Unit is to make you realise this is actually the *hardest* way of doing it!

In reality, No. 1 is best, then No. 2, lastly No. 3

Consider the following:

- it takes one person ten months to build one house

- it takes ten people one month to build one house

- it takes 100 people one-tenth of a month to build one house

Why is the last so implausible?

# Background

When there are 100 people running about they will get in each others' way; fight over limited resources like bricks; some will have to sit and twiddle their thumbs while they wait for others to finish: you can't plumb a bathroom until the bathroom has been built

And so on

And when there are more workers, you will need more managers — not building themselves but making sure workers are doing the right things

Simply adding more people won't necessarily get it done faster

Sometimes adding more people will make it go *slower* as they get in each others' way

## Background

But we can scale in a different way:

- it takes one person ten months to build one house

- it takes ten people ten months to build ten houses

- it takes one person 100 months to build ten houses

- it takes ten people 100 months to build 100 houses

This is much more believable: adding more people we can build more houses simultaneously

In reality, we won't get a perfect speedup like this, due to resource contention issues, but we can get pretty close

Most people think parallel computing is about making things go *faster*

Up to a point, but they will soon be disappointed

Much more likely to succeed is to make things larger

This scales much better

The first is *process* parallelism, also called *task* parallelism

The second is *data parallelism*

Two very different ways of getting more in a given amount of time

# Background

You all have had the situation where someone tries to help you do something and it's ended up taking *longer*

There is the basic time it takes to solve the problem: then there are substantial overheads in the coordination of the parts of the solution

The overheads can easily be larger than the problem itself

This is the reality of parallel computing

Often a parallel version of a small problem will be *slower* than the sequential version

Only when the problem is made large enough to overcome the overheads will it become faster than doing it sequentially

So cost (the number of cpu cycles) of a parallel computation = cost of computation + cost of management of parallelism

Ideally, we want the cost of management of parallelism to be minimal

But, if you are not careful, or the problem is such that this is inevitable, we can find that the cost of management of parallelism can dominate

Another huge issue is that people have enough difficulties with programming sequential machines

Some would say that sequential programming is not yet a "solved" problem

Parallel programming is *much* harder

If you think you understand parallel programing, you definitely don't

You have all the issues of sequential programs **plus** lots more

And they are issues that many programmers have difficulty even understanding

Particularly as they have been trained to program for sequential machines and have habits and assumptions that are simply invalid for parallel machines

Have I convinced you that parallel programming is difficult yet? Well, it's worse than you can imagine!

You will see the terms *parallel* and *concurrent*, with some people using them interchangeably

But it is sometimes important to make a distinction between the two

**concurrent** means your computation has separately executable parts

**parallel** means those parts are being executed *at the same time*

Concurrency is about structure, parallelism is about execution

So, "concurrent" means in parts, and those parts may or may not be running simultaneously

For example, they might be scheduled one at a time on a single core CPU)

And "parallel" when we are explicitly talking about stuff running at the same time on multiple pieces of hardware

Concurrency is about dealing with lots of things at once. Parallelism is about doing lots of things at once. Rob Pike

*Asynchronous programming* is an example of non-parallel concurrency.

This has been around for a long time in many disguises: *futures, promises, coroutines, generators* and others

The idea here is that when some code would block, e.g., waiting for some I/O, rather than the processor sitting and waiting doing nothing, the code should direct the processor to execute some other task

Later, when the I/O is ready, the processor can come back to where it was and continue from there

The code makes its own decision on what to do: moving between different parts of code, ensuring the processor is always actively working

This is scheduling *within* the code, without involvement of the Operating System

As we know, any call to the OS entails a large amount of CPU overhead, which we avoid here

These are major points of async programming: avoid OS overheads and keep the processor busy

So async code is concurrent (structural), but not parallel (execution)

Programming async code is very complicated and shares many features with programming parallel code

Modern programming languages are starting to support async programming natively, e.g., JavaScript, Swift, C++, Rust, Python and more

Constructs in the languages hide varying amounts of the gory details of choosing and switching between tasks

Async programming is good in cases where we have lots of tasks that mostly wait, e.g., I/O

Parallel programming is good in cases where we have lots of tasks that mostly compute

Async is cooperative while parallel is preemptive

Async is for *waiting* in parallel

In this unit we shall be concentrating on parallelism (though lots of what we say also applies to async programming, too)

**Exercise** Reflect on how you might use **both** async and parallel programming in one program

In contrast to concurrent and parallel, you might hear of *serial* and *sequential* both being used to describe non-concurrent/non-parallel systems

Serial and sequential mean the same thing

Why is parallelism an important topic these days?

There is a famous "law" that describes how hardware has progressed over the years

It is an **observation** on how the components in integrated circuits were shrinking over time as engineering advances were made:

#### Moore's Law (1965):

the number of transistors in a chip doubles every two years

There are a number of points to be made

- it's not a "law" in any real sense, but an *observation* on how chips progress

- Moore did not say speed doubles, as often mis-quoted

- some variants say "18 months" instead of "two years", but the history of this statement is complex

- it is somewhat self-fulfilling, as engineers tend to use it as a target for the development of each next generation of chips

There is some economics in there, too: the profit margins on silicon wafers mean that it is better to have fewer larger chips than lots of smaller chips

So CPUs tend to keep to the same area, meaning a CPU will have more and more transistors, not that we have more smaller CPUs

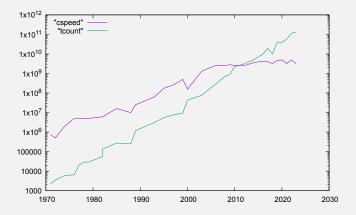

#### Background Moore's Law

Log of speed and transistor count against date of Intel processors

We can see why people thought that Moore's Law was about speed: for a long time both transistor count and speed went up exponentially

In 2005 people would have said that CPUs would be running at 480GHz by 2020

However, over the last few years speed has stopped increasing

But, crucially, the transistor count continues to increase

CPUs stay the same physical size

Engineer: What are we going to do with those extra transistors?

Marketer: How are we going to convince people to buy the new CPUs?

Solution: multicore processors

Chips with more than one CPU on them

So now chips in new PCs are all multicore

Dual and quad core is everywhere; 64 core processors are around; 128 cores are arriving soon (PC-style architecture)

Many cores is great, but we are going to have to find out how to make best use of them

But simply having two CPUs generally won't make our program go twice as fast: overheads like interference and communication between parts of the computation is going to be a problem

To repeat: all this hardware is all wonderful except for one point

This computational power is only useful if we can write the software to exploit it

Your phone might have eight cores, but it is likely very little software it runs is capable of using all their power simultaneously

Software is far behind hardware and has a lot to do to catch up

We are still in the dark regarding parallel software

#### Background A Brief Aside

Note that Moore's Law also applies to memory: memory chips have been doubling in capacity at a similar (perhaps faster?) rate

But the *speed* of delivery of data from memory to processor(s) has always lagged behind the speed of processors

Giving a problematic gap between speed of processors and speed of memory (both in bandwidth and latency)

The gap has decreased a little over the last few years, but on the other hand multiple processors need more memory bandwidth

We shall see memory is a big bottleneck in parallel systems

Moore's Law has been going for 58 years so far

It must come to an end at some point: the end has been predicted many times in the past, but so far technology has kept moving onwards

Chip designers think it will keep going for several years yet, some predict decades

Moore himself thinks perhaps it will last until 2025

And — looking at Intel's products the last few years — it might currently be taking 5 years to double transistor counts

**Exercise** Some current top end chips have over 100 billion transistors, and 7000 cores. If Moore's Law continued, how many transistors and cores would they have in 10 years? In 20 years?

Exercise Read about Moore's Second Law (aka Rock's Law)

#### Background Moore's Law

Software is getting slower more rapidly than hardware is becoming faster Wirth's Law

Software efficiency halves every 18 months, compensating Moore's law David May

The speed of software halves every 18 months Gates' Law

What Intel giveth, Microsoft taketh away Anon

There is nothing new in Computer Science and that includes parallelism. Back when large supercomputers were first popular they had been parallel for a long time

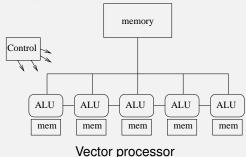

For example, a common kind of hardware was the *vector* processor

This is for data parallelism, namely scaling the data, not the speed (directly)

E.g., add together these 100 pairs of numbers to produce 100 results

A vector processor is a collection of 10s, or 100s or 1000s of fairly simple CPUs (technically not proper full CPUs, just ALUs: see later)

However, in a vector processor, the CPUs are not independent of each other: at each point in time each processor is doing the *same operation*

But on different data

So it can add 100 pairs of numbers simultaneously: data parallel

This is called single instruction multiple data (SIMD) processing

And there are other ways of making parallel machines: if you want to make a really big machine, for a long time the architecture of choice has been the *cluster*

This is "simply" large numbers of normal PCs connected together with a network, with your program spread across the nodes (the PCs)

We can get both process and data parallelism from this architecture

The hardware is commodity, so clusters with thousands of CPUs are common; clusters with millions of cores exist

Some words: be aware different people use these terms in different ways

- core: a single processing element, can be just an ALU or can have its own instruction decoding unit

- cpu: sometimes just a synonym for core, sometimes a chip which contains one or more cores

- processor: similar to cpu

- node: a motherboard that can have one or more slots for multi-core cpus that share some local resource on the motherboard, particularly memory

- cluster: a collection of nodes connected by a network

For example, the Azure machine you will be using for the coursework has four nodes, each consisting of two chips, each with 24 cores

From www.top500.org, the fastest (publicly known) computer in the world is (June 2023):

Frontier (USA), 8,699,904 cores, comprising AMD EPYC 64C cpus at 2GHz; plus Radeon Instinct GPUs; using 23MW power; with Slingshot-11 interconnect; running HPE Cray OS

This peaks at about 1.2 exaflops

1 exaflop is a quintillion  $(10^{18})$  floating point operations per second

This is the first machine to pass the "exaflop barrier"

HPE is Hewlett Packard Enterprise

Slingshot is a high performance network; a Cray technology, with (e.g.) hardware support for MPI

HPE Cray OS is a variant of SUSE Linux Enterprise Server

But lots of cores is easy: just expensive

Anyone can build a fast CPU. The trick is to build a fast **system**. Seymour Cray

The main problem in a cluster is the slow communications between the CPUs

A typical network connection is millions of times slower than a memory bus: milliseconds rather than nanoseconds

To move data from one node in a cluster to another is (relatively) immensely slow

Programming a cluster is all about moving the data: we might be able to do a million machine instructions in the time it takes to fetch some data from another node

On a machine with a million cores it can be faster to do a million adds on one core rather than ship out the adds to the CPUs; do a million adds in parallel; then collect the data back together

Just having an immensely parallel machine doesn't mean it's always better to use the parallelism

In a large parallel machine (cluster or otherwise) processing power is cheap, but data are expensive

This means you have to think about your programs differently

It might be faster to recompute the same value 1000s of times across many cores than compute it once and communicate it everywhere

A very different mindset is needed!

We need to classify the kinds of parallelism we shall be looking at

A simple classification was devised by Flynn (1966)

- Single Instruction, Single Data (SISD). Traditional, von Neumann, single core machines

- Single Instruction, Multiple Data (SIMD). As in a vector processor. Multiple cores all doing the same operation in *lockstep*, but on different datastreams

- Multiple Instruction, Multiple Data (MIMD). Multiple cores doing different things to different datastreams. What most people (wrongly) think parallel computing is all about

• Multiple Instruction, Single Data (MISD). Something to fill in the last combination of letters. Sometimes interpreted as *redundancy*, e.g., airplane flight control where they have multiple (different!) computers all processing the same data

|          |          | Data   |          |

|----------|----------|--------|----------|

|          |          | Single | Multiple |

| Instruc- | Single   | SISD   | SIMD     |

| tion     | Multiple | MISD   | MIMD     |

Flynn's classification is nice and simple, so people have extended it further, in particular sub-dividing MIMD

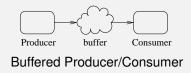

- Single Program, Multiple Data (SPMD). Recall SIMD runs the same program on multiple cores in *lockstep*, so every core is executing the same instruction. SPMD runs the same program (on different data) on a MIMD machine, with each core going their own way, particularly on loops and conditionals

- Multiple Program Multiple Data (MPMD). A MIMD machine not running SPMD. So each core running potentially different programs, e.g., producer-consumer models, or systolic pipelines (see later)

Of course, there are many more classifications we need to look at

We can think of how the parts of the architecture are connected

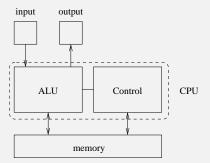

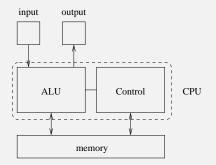

Uniprocessor

A *uniprocessor* (*unicore*) or *sequential processor* is the traditional von Neumann architecture of a single CPU, memory, etc.

von Neumann Architecture

A hugely successful model that enabled the computer revolution to take place

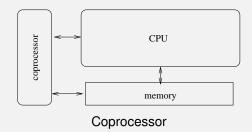

#### Classifications Coprocessor

A *coprocessor* is a non-general processor used as a worker by the processor

Currently very popular in the form of graphics cards

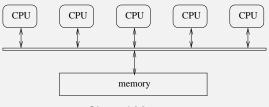

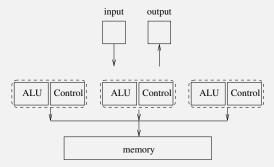

**Multiprocessor**

A *multiprocessor* is a loose term applying to most parallel architectures, except occasionally SIMD, which usually doesn't have multiple full cores

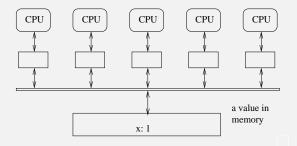

A multiprocessor has *shared memory* when the cores access memory on a shared bus

Shared Memory

Cores share each other's data: if one core modifies the value of a value in memory, the other cores see that change

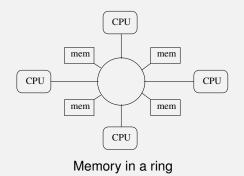

In reality, the shared bus can be a lot more complicated, e.g., a tree or ring structure

In this example, we have *symmetric* shared memory: every CPU has the same equal access to the shared memory

This is possibly what most people think of as a typical parallel architecture

Unfortunately, it has a lot of problems as an architecture

In particular, the memory is a bottleneck

Memory and memory buses are slow relative to a processor anyway, and when you have several cores all trying to access memory simultaneously it gets much worse

Shared Memory

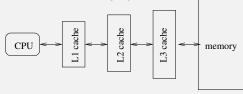

Even single core processors have a problem with the speed disparity, so they use fast (but small) intermediate cache memory

A small (because it's expensive) chunk of very fast memory where you store copies of a few of the values you are currently using from main memory

Sometime two or three (occasionally four) levels of cache of increasing size but decreasing speed

Levels of cache

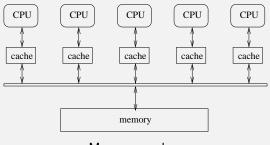

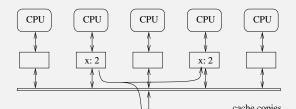

So shared memory machines try to cut down the traffic on the bus by using caches

Memory caches

Each core has its own chunk of fast cache memory: this cuts down on use of the bus

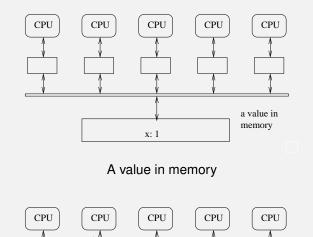

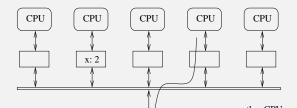

#### Shared Memory

If a core is manipulating the value of a variable it will be loaded into the cache and operated on there, rather than over the bus in main memory

This reduces pressure on the shared bus: but now we have the problem of *cache coherence*

A CPU only updates its cached copy; the global copy remains at its old value for a while

So if another core want to read the value before the updated version has been written back, it will get the old value

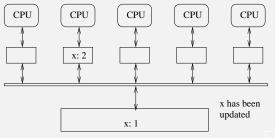

#### **Shared Memory**

#### x has been updated in cache

Shared Memory

Even worse, dependent on timing, you don't know if the first CPU has written the value back or not

Meaning different runs of the same program can produce different results, dependent on what else happens to be going on in the system

This is an example of a *race condition*: differing orders of execution of concurrent parts of a system produces varying outcomes

This particular example is a *data race*: a race condition that involves updating data

Not what we want, as we can't control the vagaries of hardware operation

You might get the right answer on hundreds of runs; it doesn't mean your program is correct!

And it might always happen to be right on your machine, but wrong when run on some other machine

There are other ways to fail, too

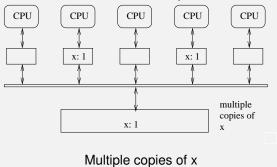

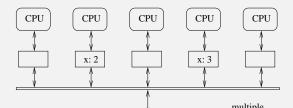

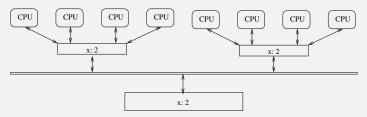

Others cores might be doing the same: reading and updating the value. Thus there can be several conflicting copies of what is supposed to be the same variable in different caches

When one core updates the variable the other cores will still be using their own in their caches

#### **Shared Memory**

The *cache coherence* problem is the issue of trying to make sure all cached copies of a variable are kept in sync

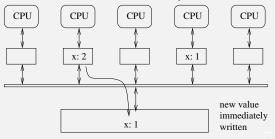

This might be done in several ways

E.g., in the *snarfing* protocol, whenever an update is made the value is immediately written through the bus (increasing traffic on the bus...) to main memory. The other caches are watching the bus and if they have a copy of the variable they update their copy with the value being written (they "snarf" the new value)

This is expensive in hardware and does not scale well to large number of cores as every write must go through the bus

#### **Shared Memory**

#### New value immediately written to memory

But this is better than you might imagine as typical code reads values much more than it updates values

$\ln x = y + z$  two values are read, one is written

So this kind of cache-watching is more effective than you might think

Secondly, well-written code will avoid using shared values in the first place. Sharing mutable state across threads is bad design (more on this later)

Other solutions might be to try to balance the memory/cpu speed disparity

You could use very fast buses and main memory: not a solution due to cost

Or use slow processors: IBM tried this and it was surprisingly good!

**Exercise** Modern architectures are more like:

Modern memory architectures

Does this solve the problem?

Unfortunately, such *symmetric* shared memory does not scale well, perhaps a few 100s of cores, with complex hardware support in the caches

Ampere has a 128 core Arm architecture

Intel have just announced a 288 core x86 chip (Sept 2023)

**Exercise** Read about cache coherence mechanisms: snoopy caches; directory based; snarfing; MSI; MESI

**Exercise** Another complication to symmetric shared memory is when the *cores* are not identical: read about *performance* and *efficiency* cores (P-cores and E-cores) used by Intel, Apple and others

Symmetric shared memory is the model that current small machines (multicore PCs) use

It is well suited to MIMD, but note that SIMD also uses symmetric shared memory, but with a different access pattern

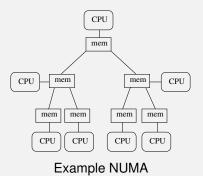

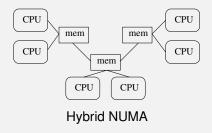

So if symmetric, i.e., uniform access, shared memory does not scale, we can try managing memory in other ways

Each processor has a chunk of memory, but can also access memory of other processors, perhaps arranged in a tree

A processor will have fast access to its closest chunk of memory, but slower access to more remote memory

And different chunks of remote memory will have different access speeds

Of course many other topologies have been tried: star, ring, hypercube, full interconnect, and so on

This architecture evens out the access time to different chunks of memory a little

These are *non-uniform memory access*

NUMA shared memory scales much better than symmetric shared memory

By scaling here we mean you can build larger machines with more processors cost effectively

But there is a downside: now programs and programmers (and the OS) have to worry about *data locality*: data a processor needs should be kept close to that processor

It can make a huge difference to the speed of a program if the data is not where it should be

If data is close to the processor that is using it, it will go faster than if the data has to be fetched from further away

So you try to keep data near the relevant processor

Or the computation on a processor near to the data

Of course, if data needs to be used by several processors, this becomes a very difficult scheduling problem

NUMA implementations stratify the memory in terms of "distance"

For example:

- direct connection on the local memory bus

- on the same node

- one hop away

- two hops away

- and so on

Though this is often simplified to: local, remote, and "far away"

The OS or system libraries or the programmer will try their best to place data in appropriate memory to minimise latency, using their knowledge of the NUMA hierarchy and their knowledge of the program's needs

The programmer ideally would have a good idea of the architecture of a machine before writing code for it

And so the portability of a program is in question

This is still a matter of great research and development!

And, of course, there are hybrids where CPUs share some memory symmetrically and some memory NUMA

NUMA allows architectures to scale to greater numbers of processors, but it won't scale indefinitely, perhaps a few 1000s of cores

If the problem is the memory bus bottleneck which means you have to keep cached copies of a value, and then you have the problem of keeping coherence amongst the copies, why not simply *not* have shared memory?

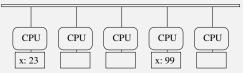

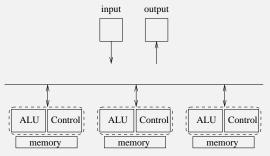

*Distributed memory* says each processor's memory it its own and is entirely separate from every other processor's memory

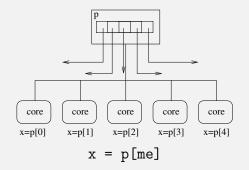

**Distributed Memory**

Shared memory processors share a *single memory address space*: within a single process memory location 42 on one processor refers to the same thing as memory location 42 on every other processor, as it's the same memory

The variable x on this processor is the same as the x on that processor (assuming SPMD)

**Distributed Memory**

Shared address space

**Distributed Memory**

Processors in a distributed memory architecture each have their own, separate, address space

Memory location 42 on one processor is entirely separate from memory location 42 on every other processor

Each processor has their own version of variable x, nothing to do with any other x on other processors

**Distributed Memory**

#### Each processor has its own memory

Network

Distributed memory architecture

Typically connected by a network, rather than an expensive memory bus

**Distributed Memory**

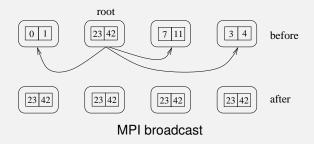

To get at data on another node a processor sends a *message* to that node, which will reply with the data

Clearly this *message passing* will be very much slower than simple shared memory accesses

Memory access across a network can be factors of thousands, perhaps millions times slower than local memory

The position of data is now very important

Your code has to change, too

**Distributed Memory**

Think of a shared memory operation:

```

x = y;

x gets the value of y, "simply" read from memory

```

Compared with the overhead in distributed memory of creating a message, sending, waiting, reading the reply

See MPI (Message Passing Interface) later, but conceptually we have to write

```

x = FetchDouble(remotecpuname, "y");

```

**Distributed Memory**

Some underlying message passing library does the hard work of the messaging

Your code become much more complex to write

Both in needing a lot more text, and in needing thought on where to put your data

Message Passing

Note that you can also use message passing on a shared memory architecture

Doing so might be useful for coding or program structure reasons

The underlying messages are now probably implemented as simple accesses to shared memory

Some parallel programming systems (see later) *only* provide messaging across threads (often via mechanisms called *channels*), thus masking the underlying architecture and improving program portability across architectures

Distributed Memory

When using distributed memory you try to keep the data a process needs on the processor it is running on, maybe even replicating data or replicating computations, and access remote data as little as you get away with

You have to balance the cost of the computations against the cost of the data movement

An ideal that is rarely achieved in real programs

Of course, if you replicate data that gets updated, you immediately have a coherence problem again, but now your own code has to deal with it

**Distributed Memory**

Note that replicating read-only data (e.g., tables of values) will be fine: there is no coherence issue with multiple copies of data that never changes

But you do need to put a lot of thought into replicating read-write (mutable) data

More sophisticated systems have extensive hardware support for messaging

They have specific *direct memory access* (DMA) hardware that accesses memory independently of the CPUs

Thus messaging proceeds independently of the CPU: communication is *asynchronous* with computation, freeing the CPU to do something else while the message is being processed by the DMA hardware

Thus allowing more computation; but at the cost of more complicated programming

Computation vs. Communication

The call to FetchDouble above could return immediately and allow your code to continue computing on something else, rather than waiting for the value of y to appear: but you can't use x until the value has arrived some time later

Of course, you now need some mechanism to be notified when the value has arrived, and so you can now use  $\mathbf{x}$

Such asynchronous programming is very hard to get right

But this idea of overlapping computation and communication is important and will reappear many times

#### Classifications Distributed Memory

In distributed systems the concept of single shared values has to go completely out of the window

The value of  ${\bf x}$  here is nothing to do with the value of  ${\bf x}$  there

Programs have to be written with this in mind: global shared mutable values are simply not a good idea, even in uniprocessor programs!

**Distributed Memory**

Distributed memory is the architecture used by clusters: each node is effectively a PC

Very suitable for SPMD, not so suitable for SIMD

Even with the huge message passing overhead, clusters are very popular, particularly with very large problems where the overhead is small relative to the rest of the computation

The computations do have to be huge!

**Distributed Memory**

Not suitable for small problems, or problems where data need to move a lot between processors

Scales *very* well as an architecture. Clusters of over a million cores exist: see the TOP500 list

#### Classifications Scaling

Making big machines is easier with distributed systems, too

When we try to add CPUs to a shared memory system, we have to pay a great deal for the complicated memory architecture as it means redesigning the silicon and building new chips

This can quickly swamp all other costs, so making scaling a shared memory system impractical

In contrast, the cost of adding CPUs to a distributed memory system is "simply" the cost of the CPUs and the networking

This is roughly linear (per CPU) price scaling

However, when scaling a cluster we should take care to scale the network, too, otherwise we have exactly the same kinds of bottleneck issues that shared memory systems have

In a network like

Simple shared network

the single shared network is clearly a bottleneck

#### Classifications Distributed Memory

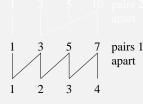

So we need to scale the network. There are many choices:

Network with two interfaces

Each processor would use one interface to communicate with processors 0, 2, 4, etc.., and the other interface to processors 1, 3, 5, etc., thus spreading the load

**Distributed Memory**

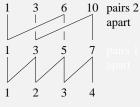

Or three interfaces

Network with three interfaces

But this gets expensive very quickly

**Distributed Memory**

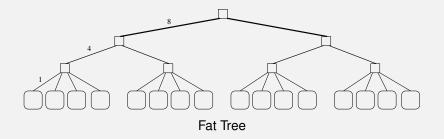

Trees are a good way of connecting things:

Though the upper links now are a bottleneck, and we have introduced another non-uniformity

**Distributed Memory**

In a *fat tree* links up the tree have larger bandwidths, thus allowing full simultaneous bandwidth between each pair of nodes

**Distributed Memory**

Though the latency between nodes will vary

In practice, a full fat tree is quite expensive, so real fat trees tend to skimp on the upper links a bit, e.g, 1, 2, 2 in the above diagram would be much cheaper to build (and a "2" would probably be a pair of "1"s)

Thus trading bandwidth for cost

Many other topologies exist, such as hypercube, torus, Banyan, etc.

**Exercise** Azure uses a *Clos network* within its datacentres. Read about this

**Distributed Memory**

The point here is that this is relatively cheap to do with a distributed memory network. But adding bandwidth by doing this kind of connectivity in a shared memory system is extremely expensive as it likely needs new silicon

Adding bandwidth in a network is relatively cheap

But decreasing latency is very expensive whatever the system

Virtual Shared/Distributed Virtual Memory

Some programmers don't like the fact that distributed memory machines require programming using message passing and prefer the shared address space model: shared memory is easier to write programs for (they claim)

They can use virtual shared memory

Just as virtual memory is a way of converting virtual memory addresses into physical memory addresses, virtual shared memory is a mechanism to have a single, virtual, address space that is converted into distributed physical addresses

Thus this is also called *distributed virtual memory* and *distributed shared memory*

Virtual Shared/Distributed Virtual Memory

Reading and writing variables will be implemented by a message passing layer hidden from the programmer in the OS or systems libraries

So the programmer won't have to care about it and they can write programs as if the whole of memory was one big chunk

The programmer writes the simple "x = y" and the compiler/OS converts this into a shared memory access or a message call as appropriate

But it will be very NUMA to data

Virtual Shared/Distributed Virtual Memory

Unfortunately, programmers *do* have to care as the speed of a program will be very hard to predict or control, depending on how data is distributed across memory and the particular NUMA architecture it is running on

How long does the assignment "x = y" take? Is it different from "x = z"?

A good programmer looking for a good, consistent performance from their code will still need to think hard

A poor programmer will think their life is easier

Virtual Shared/Distributed Virtual Memory

The underlying system also needs to solve all the problems of cache coherence that shared memory hardware has, but now using the (relatively) slow messaging passing layer rather than custom-designed hardware

The NUMA aspect is so unpredictable that many programmers prefer to be in control and have an explicitly non-shared model

When you write FetchDouble you know it is going to be slow

Compare with "how fast is x = y?" in VSM

Virtual Shared/Distributed Virtual Memory

The underlying communications layer in VSM might be implemented

- in the Operating System, such as *Mosix*. This means all standard system libraries and user code can be used unchanged and a cluster looks like a single big machine: a *single system image* (SSI)

- by the programming language and libraries, such as Cluster OpenMP or Unified Parallel C (see later), so the language may need a bit of learning by the programmer

Virtual Shared/Distributed Virtual Memory

VSM is currently fairly rare in practice, though as NUMA techniques improve, people are starting to talk about *shared memory clusters* as being a viable and useful way to proceed

### Latency numbers every programmer should know

| L1 Cache hit                          | 0.5 ns         | 0.5 sec<br>one heart beat                         |

|---------------------------------------|----------------|---------------------------------------------------|

| Mutex lock/unlock                     | 25 ns          | 25 sec<br>making coffee                           |

| Main memory access                    | 100 ns         | 100 sec                                           |

| Read 1MB from memory                  | 250,000 ns     | brushing your teeth<br>2.9 days<br>a long weekend |

| Round trip within                     | 500,000 ns     | 5.8 days                                          |

| datacentre                            |                | a short holiday                                   |

| Read 1MB from disk                    | 30,000,000 ns  | 1 year                                            |

| Send a packet California $ ightarrow$ | 150,000,000 ns | 4.8 years                                         |

| Netherlands $\rightarrow$ California  |                | two round trips                                   |

|                                       |                | to Mars                                           |

https://gist.github.com/hellerbarde/2843375

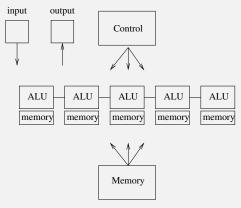

The next class of architecture is one we have already touched on

It has elements of both shared and distributed memory

It is used for data parallel computation

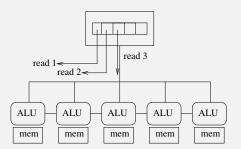

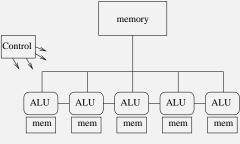

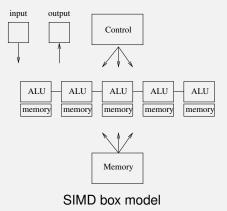

A *vector processor* is a SIMD collection of CPUs (actually ALUs), often with a chunk of global shared memory (and a single control unit)

Each processor also has its own chunk of local memory that it operates on

The local memory allows each ALU to work on a different set of values

Note: this is not cache, but simply per-ALU memory

Cache vs Local

Cache memory: a fast local copy of a slower memory location. If a value of a variable is cached on different cores, we want all the caches to contain the same value for that variable

Local memory: per core memory (not always fast, by the way!) where we expect to have different values for a given variable in each

In a vector processor, the bottleneck to the shared memory still needs thinking about

For reads: as the cores are all doing the same thing, if one requests a global shared value from a fixed shared memory location, then all of them are doing the same

So the memory system puts that single value on the bus and all the cores read it: no bottleneck

Sometimes called a broadcast

#### Classifications Vectors

ALU ALU ALU ALU ALU MEM MEM MEM

One read goes to all cores

#### Classifications Vectors

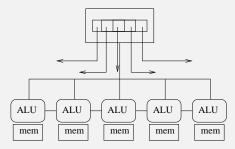

However, as is often the case, it can be that each core wants a value from a different part of global memory. E.g., core k wants the kth element from a array

Reading a vector of values

In this case, it takes careful management, both by the hardware and by the programmer, to ensure the transfers use the shared memory bus efficiently

The case of sending the sending the *k* item to the *k*th core is often optimised by the hardware using *coalescence*

Using a wide bus (e.g., 512 bits) a *single* read operation can fetch multiple data (e.g., 16 integers) and put them all on the bus simultaneously

Each core reads the value it wants

The next 16 values are sent in the next transfer; and so on

#### Classifications Vectors

ALU ALU ALU ALU ALU mem mem mem mem mem

A single fat read goes to multiple cores

However, it needs data accesses in the program to be of certain patterns for this to work, e.g., linear access to an array

The kinds of access pattern allowed for coalescence are dependent on what the hardware supports, but are generally picking some subset of a contiguous chunk of the shared memory

Otherwise, the reads cannot be coalesced and might require many (e.g., 16) individual reads: much slower

E.g., proc k wants value  $k^2$  from the array

#### Classifications Vectors

Awkward distribution done in multiple reads

Similarly for writes: e.g., core k writing a value to the kth slot in an array could be coalesced

Multiple writes to a single location make no sense and are often disallowed by the system

**Exercise** Consider the case of indirecting through a pointer to global memory (a) when each core points to the same location and (b) when each core points to a different location in the global memory

**Exercise** Consider the case of indirecting through a pointer to local memory (a) when it's pointing to the same location on all cores and (b) when it's pointing to a different location on each core

Vectors

Often there is fast direct communications between neighbouring CPUs

Neighbour connections

This allows data to shuffle up and down the vector very quickly: many problems (e.g., differential equations solving) work on data and neighbour data in this way

Clearly, vector processors are SIMD and not suitable for MIMD or even SPMD

Vector processors appeared early in parallel computing as they are relatively easy to build: ALUs are relatively easy to build and replicate, while control units are complex and hard

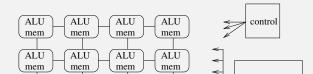

Arrays

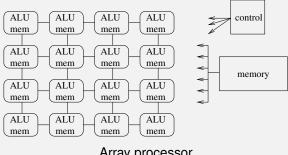

An extension of the idea was the array processor

The CPUs are in SIMD lockstep as before, but now in an array Fast connections in two or more directions

This fits well with 2 dimensional differential equation problems

More expensive than vector processors and much less common

#### Classifications Arrays

Early array processors were very simple, but they became bigger as technology advanced

|          |      | CPU    | #CPUs | mem/CPU |

|----------|------|--------|-------|---------|

| DAP      | 1979 | 1 bit  | 4k    | 4k bits |

| CM       | 1983 | 1 bit  | 64k   | few kB  |

| MPP      | 1983 | 1 bit  | 16k   | 1 kB    |

| MasPar   | 1990 | 4 bit  | 16k   | 16kB    |

| MasParll | 1992 | 32 bit | 64k   | 64kB    |

DAP: ICL Distributed Array Processor CM: Connection Machine (pretty lights) MPP: Goodyear Massively Parallel Processor

Despite being very wimpy processors, this was made up by having so many of them

Their throughput (results achieved per second) is quite respectable

They work very well for certain kinds of problem (e.g., weather forecasting), but are not suited to many other kinds of problems

Vector/array processing processors are important due to their influence on the design of GPUs

Shared, distributed and vector processors are the three major architectures used today

But others have been tried, with varying levels of success

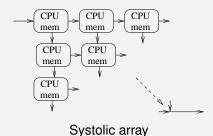

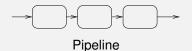

Pipelines, Systolic Arrays

Similar looking to vector processors, but actually quite different, are *systolic arrays*

These generalise CPU instruction pipelines to processes

Process pipeline

The CPUs are independent (MIMD/MPMD), each performing one step in the transformation of the input data

More often found in hardware to solve specific problems; not often found as a generic machine

**Exercise** Could this be classified MISD?

Pipelines, Systolic Arrays

For example, a graphics card might want to do clipping of polygons, then colouring, then shading

Each step separate, but compute intensive

Just as pipelining instructions in a processor allows instructions to be processed faster, pipelining these kinds of computations allows pixels to be computed faster

Used in graphics coprocessors as another form of parallelism

Part of the reason why digital TV is delayed relative to realtime is that the encoding of the picture goes through a big pipeline before it is transmitted: there is an inherent *latency* in pipelines

Pipelines, Systolic Arrays

Systolic arrays are the obvious extension

but it is unclear if these were ever built

Extensions of von Neumann

So why do all these varieties of parallel architecture exist?

There is essentially just one way uniprocessor machines are built: the von Neumann model

Is there a model that encapsulates multiprocessors in the same way?

There are many contenders, but no obvious winner

Extensions of von Neumann

#### We have the original von Neumann 5 box model

von Neumann 5 box model

Extensions of von Neumann

#### Shared memory MIMD

Shared memory box model

Extensions of von Neumann

#### Distributed memory MIMD

Distributed memory box model

#### Extensions of von Neumann

#### Vector processor

Vector processor memory box model

Extensions of von Neumann

Perhaps there just isn't a single extension of von Neumann that is suitable as a one-size-fits-all solution

Or perhaps we just haven't thought of it yet?

Extensions of von Neumann

There are several theoretical models whose aim is to guide the design of parallel algorithms and allow the analysis of them

As with von Neumann, the idea is that you

- write your program in accordance with the model

- the model maps well onto all kinds of real hardware

- therefore your program maps well onto all kinds of real hardware

Extensions of von Neumann

Firstly: **PRAM**

The *Parallel Random Access Machine* model idealises a parallel computer as shared memory MIMD, concentrating on the memory bottleneck

You have a choice of how memory can be accessed:

- *Exclusive Read Exclusive Write* (EREW). Each memory location can only be read or written by *one* processor at a time. The simplest architecture

- Concurrent Read Exclusive Write (CREW). Each memory location can be read by many processors simultaneously, but written by just *one* processor at a time (c.f. global memory in a vector processor)

Extensions of von Neumann

- Concurrent Read Concurrent Write (CRCW). Each memory location can be read or written by *many* processors simultaneously. Not a realistic model

- *Exclusive Read Concurrent Write* (ERCW). The fourth combination, never used.

Extensions of von Neumann

PRAMs make many further simplifying assumptions, including:

- Memory is symmetric: every location is accessed at the same speed. Decreasingly realistic

- There are an unlimited number of processors: there's always another processor if you need it. Seems unrealistic, but not so bad as you think as most programs are unable to make use of the hardware that we currently have

- Memory is unlimited. This assumption is also often made in analysis of uniprocessor algorithms

Extensions of von Neumann

In the early days of Computer Science, there were many clever algorithms invented to deal with the lack of available memory

And, to some extent, memory is still limited in some modern architectures that have very large numbers of CPUs so proportionally each has only a small share of memory

And people want to run programs on datasets of ever-increasing size

Extensions of von Neumann

So you analyse your program, counting numbers of memory accesses it makes (according to which of EREW/CREW/CRCW you have chosen) and this gives you a measure of the time your program will take to run

This is primarily a MIMD model, but you can analyse SIMD using it

It totally ignores important realities like NUMA and other overheads, such as communication time in a distributed memory system

But it gives you a rough idea and it is extensively used in analysis of parallel algorithms: we'll have some examples later

Extensions of von Neumann

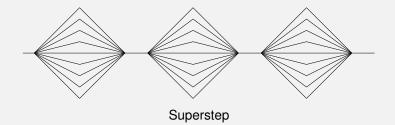

Next: **BSP**

The Bulk Synchronous Parallel model

This model takes communication time into account

It assumes processors with local memory communicating over a network

Good for distributed, but can be used for shared memory where you just have smaller communication costs

Extensions of von Neumann

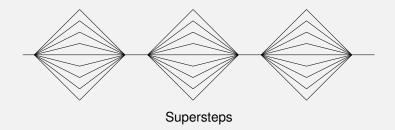

A computation is modelled as a sequence of *supersteps*

- each processor does some computation (MIMD, but could be SIMD)

- each processor does some communication

- each processor waits at a global *barrier* until everybody has finished their communications. This is the "bulk synchronous" part

- repeat

Extensions of von Neumann

**BSP** supersteps

Extensions of von Neumann

Processing is simplified in this way to give us a chance of being able to make an analysis

Fortunately, many real computations are not too far from this shape

More realistic than PRAMs, but harder work to get analyses out of it

But those analyses tend to be a better match to realistic hardware

Extensions of von Neumann

And so on for many other models, some practical, some not

For example, parallel Turing machines and *Communicating Sequential Processes* (CSP) amongst others. Both better at describing the nature and limitations of parallel programs than for investigating how well they work

But the fact remains that there is not one simple theoretical model that works well for all kinds of parallel processing

This might be the source of the confusion in parallel hardware, but we have to live with it

### Analysis

So we need to look at how to analyse parallel algorithms

Analysis of parallel algorithms is like analysis of sequential algorithms, just more complicated

Later we shall see statements like "this takes time  $O(n^2)$  using O(p) processors"

But we shall start with a few simple measures that we can use to indicate how well our parallel algorithms are working

They are quite crude, but effective

#### Analysis Speedup

They mostly measure the parallel algorithm in comparison with a corresponding sequential algorithm

Or a parallel *implementation* with a corresponding sequential implementation: by timing actual running code

We have seen that having p processors won't necessarily make our program run p times as fast

The *speedup* using *p* processors is

$$S_p = rac{ ext{time on a sequential processor}}{ ext{time on } p ext{ parallel processors}}$$

Ideally we'd like  $S_p = p$ , but this never happens

Usually  $S_p$  is much smaller than p for several reasons

Firstly, there is communications overheads between processors

This might be fairly small for shared memory, or large for distributed memory, but it is present

Time spent communicating is time not spent computing

So more communications (data movement) will tend to lead to smaller speedups

For example, speedups on distributed memory machines can be reduced as the cost of communications is quite high

But speedups can improve for a larger computation where the *relative* cost of communications drops

Remember clusters are used for large problems where the emphasis is on size, not speed

In really bad cases,  $S_p < 1$ , i.e., our parallel program goes *slower* than our sequential program even though we've thrown all this expensive hardware at it!

This is more common than we'd like

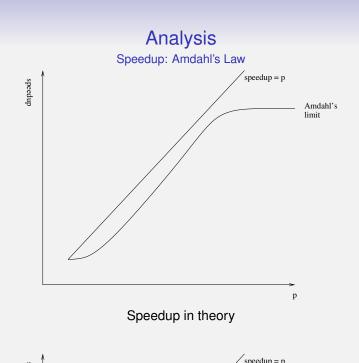

#### Analysis Speedup: Amdahl's Law

Now there is the natural upper bound of  $S_p \le p$ : we wouldn't expect to get more speedup than the number of processors we have

But it turns out that the number of processors is generally not the limiting factor on speedup: there is another fundamental restriction on speedup that is often overlooked

*Amdahl's Law* reveals a natural upper bound on the speedup that is theoretically possible even before we add in implementation overheads

#### Analysis Speedup: Amdahl's Law

Suppose we have a problem of which 90% can be run in parallel, leaving 10% sequential code

For example, we have to read data before we can process it: a necessary sequentiality. Similarly for writing after processing. Or the add after the square in  $x^2 + 1$

So there's always some sequentiality

But in the best possible case, using an unlimited number of processors, we might be able to get the parallel part down to as close to zero time as we like

We still have the 10% sequential part

#### Analysis Speedup: Amdahl's Law

So the speedup is

$$S_{\infty} = rac{ ext{time on a sequential processor}}{ ext{time on parallel processors}} = rac{100}{10} = 10$$

A speedup of 10 even on an infinite number of processors

It doesn't even matter what the problem is, or what hardware we have

This is Amdahl's Law:

Every program has a natural limit on the maximum speedup it can attain, regardless of the number of processors used

We can quantify Amdahl's Law:

Let  $T = T_{seq} + T_{par}$  be the time spent in the sequential and parallel parts of our problem on a sequential processor

Then the *maximum* speedup  $S_p$  using *p* processors on the parallel part is

$$\mathcal{S}_{\mathcal{p}} \leq rac{\mathcal{T}_{\mathsf{seq}} + \mathcal{T}_{\mathsf{par}}}{\mathcal{T}_{\mathsf{seq}} + \mathcal{T}_{\mathsf{par}}/\mathcal{p}}$$

where we have perfectly parallelised the parallel part

Thus there is a natural upper limit on how fast programs can go Most do I/O, which must be serialised (made sequential)

Further, as  $p \to \infty$ , we get

$$S_{\infty} \leq rac{T_{ ext{seq}} + T_{ ext{par}}}{T_{ ext{seq}}}$$

so there is a limit even given infinite processing power

This limit is determined by the time taken in the sequential part of the computation

To see this consider the fraction  $x = T_{seq}/(T_{seq} + T_{par})$  which is the proportion of the sequential part within the whole

Note that  $0 \le x \le 1$ , and that rearranging the above gives

$$S_p \leq rac{1}{x+(1-x)/p}$$

And so

$$S_{\infty} \leq \frac{1}{x}$$

4

is bounded

# Note that Amdahl does not say anything about how the speedup varies with p

All Amdahl says is that an upper limit exists

Your program may not get anywhere close to that limit and often in real programs, does not

In real programs, there are many other factors that affect speedup, so that the speedup may well vary all over the place as p increases

It can even decrease as p gets larger

To emphasize: all we know is that actual speedup is below Amdahl's limit

**Exercise** Show that if  $0 \le x \le 1$ , then

$$\frac{1}{x+(1-x)/p} \le p$$

**Exercise** What is the maximum speedup of a program that is 100% sequential?

#### Analysis Speedup: Gustafson's Law

Amdahl's law is real: there is a natural limit on speedup for a given problem

But there's another point of view

Gustafson pointed out that in real life larger machines tend to attract larger problems

Amdahl assumes a fixed size of problem

*Gustafson's Law* (occasionally called *Gustafson-Barsis's Law*) gives us another limit

## Analysis

Speedup: Gustafson's Law

Suppose we have a problem of size *n*

$$\mathcal{S}_{p}(n) \leq rac{1}{x_n + (1-x_n)/p}$$

where  $S_p(n)$  is the speedup on *p* processors for a problem of size *n*;  $x_n$  is the fraction of the computation spent sequentially

Gustafson argues: as *n* gets larger, the sequential part relatively decreases, so  $x_n \rightarrow 0$  (*p* is fixed)

So

$$S_{

ho}(\infty) \leq

ho$$

i.e., we now get a speedup limit that is the "perfect" speedup p — on an infinitely sized problem

### Analysis

Speedup: Amdahl's Law, Gustafson' Law

Both Amdahl and Gustafson are correct: they just apply to different cases of scaling

Amdahl: fixed problem, scaling processing power (sometimes called *strong scaling*)

Gustafson: fixed processing power, scaling problem

This should convince you that even a simple measure like speedup can be problematic!

But it does re-emphasise the fact that parallelism is not about making things faster, but about making things larger

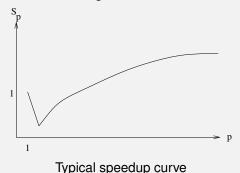

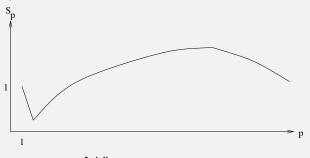

Speedup is a simple measure, often proving that your parallel program is slower than it ought to be

Sometimes it takes *p* to be surprisingly large before you even catch up with the uniprocessor time with  $S_p = 1$  (sometimes never!)

Very common is the low start, a modest increase, then a tailing off

But taking it further

Adding more processors

We might eventually find adding processors makes it slower!

This is usually due to increased communications between the processors adding more overhead but not more speedup, perhaps due to Amdahl

Of course, it's not always this bad, but it's quite common!

It does mean there is often an optimum number of processors for a given size of problem that achieves the best speedup

Of course, these are only typical behaviours: a given program may behave quite differently from all of this

**Exercise** Consider what might be the difference between a sequential implementation of something and a parallel implementation running on one processor

You will get used to seeing  $S_p < p$

On the other hand, it is possible that  $S_p > p$

This seemingly impossible condition is called *superlinear speedup*

It is quite rare in real life, but it really can happen that a program runs more than p times as fast on p processors

This can happen for a variety of reasons, some technological, and some more philosophical

The first technological reason is due to cache memory

Cache memory is a lot faster than main memory so if you can fit your problem entirely in cache, it will run faster

For example, a Core i7: perhaps 200 cycles to access main memory, compared to 2 cycles for a L1 cache hit

*p* processors might have *p* times the cache of a single processor, so a problem spread across the processors might well fit in the larger amount of cache available

Of course, this takes a certain kind of low-communication, easily dividable problem to work; and the right hardware

Note: modern CPUs tend to share cache across multiple cores, so it is unlikely *p* cores has *p* times as much cache

(This helps with cache coherence!)

Another (more philosophical) reason is due to the way speedup is defined

$$S_p = rac{ ext{time on a sequential processor}}{ ext{time on } p ext{ parallel processors}}$$

What are we comparing against what?

Here is an example to illustrate the issue

We have bubblesort running on a uniprocessor: we wish to make it run on a parallel machine

One way of doing this is:

- split the data into equal halves

- bubblesort each half in parallel

- merge the two sorted lists together

This is 2-way parallelism

The middle step can be itself parallelised recursively: split into two, bubble and merge, giving 4-way parallelism

Depending on the number of processors we have, we can keep recursively dividing

This seems like a reasonable way to implement bubblesort on a parallel machine

What is the speedup? We need to find out how long each version takes to run

Normal bubblesort takes time  $n^2/2 + O(n)$  comparisons in the average case to sort *n* items

So bubblesorting the two halves (in parallel) takes time

$$(n/2)^2/2 + O(n/2) = n^2/8 + O(n)$$

Merging n values takes O(n), giving a total of

$$n^{2}/8 + O(n) + O(n) = n^{2}/8 + O(n)$$

time

This gives speedup

$$S_2 = rac{n^2/2 + O(n)}{n^2/8 + O(n)} pprox 4$$

Already superlinear!

On 4 processors we could repeat: the speedup we get is  $\mathcal{S}_4 \approx 16$

Clearly this a wonderful algorithm

If we were to implement it, we would truly see these speedups

What is happening?

Consider the same subdividing algorithm on a single processor

Time to bubblesort halves:  $2 \times (n^2/8 + O(n)) = n^2/4 + O(n)$ ; time to merge O(n); total  $n^2/4 + O(n)$

"Speedup"

$$S_1 = rac{n^2/2 + O(n)}{n^2/4 + O(n)} pprox 2$$

So we win even on a uniprocessor

What is happening is that bubblesort is a really poor sorting algorithm on average

By subdividing and merging we are converting it into a different kind of sort: if we recurse all the way we have actually implemented a *merge* sort

Merge sort has complexity  $O(n \log n)$

The point of this is that by converting bubblesort to be parallel in this way we are fundamentally changing it

This is an extreme case, but in general we must be care when computing speedups that we are comparing like with like

It may not always be possible to have a suitable parallel version of an algorithm: in such a case "speedup" is not meaningful

In most real cases we don't get this effect, but it's worth being aware that it can happen

Some people go further and define speedup as

$S_p = rac{ ext{time of the best possible sequential algorithm}}{ ext{time on } p ext{ parallel processors}}$

but this has its own problems, not least that we might not know the best possible sequential way of doing things

And we now might be comparing two completely unrelated algorithms

In a similar vein, another reason for getting superlinear speedups is that the original, sequential, program was poorly written

Perhaps the programmer spent more time thinking about the parallel version, or gained more experience from writing the sequential version, making it substantially better code than the sequential version

This is much the same as the "transform bad algorithm to better algorithm" above, but is now "transform bad code to better code"

So, again, we are not really comparing like with like

And occasionally we see superlinear speedup due to randomness

If the data contains random numbers, or there is something that adds an elements of randomness to the run time we can get a superlinear speedup

This time due to the parallel version "getting lucky" and hitting a special case that finishes early relative to your measured sequential version

So also not comparing like with like

You would need to ensure each run had the same randomness to be properly comparable; or run many times and take an average time

In conclusion: speedup is a nice and simple, easy to understand measure: but we have to take care over what it is telling us

Some problems are *pathologically parallel*, meaning they fall easily into parallel parts that have a minimum of communication

For such problems it is easy to get good speedups

E.g., graphics rendering, weather forecasting, parameter sweeping, etc. Often they are data parallel problems

Other problems fare less well — in terms of speed — from parallelisation!

If we are lucky enough that  $S_p$  increases with p we can make our program get faster by adding more processors

But at what cost?

If we can double the speed of a program using 4 processors we feel we are doing better than if we used a different approach that needed 8 processors for the same speedup

Efficiency measures this

#### Analysis Efficiency

Efficiency is speedup per processor:

$$E_{p} = rac{S_{p}}{p} = rac{ ext{time on a sequential processor}}{p imes ext{ time on } p ext{ parallel processors}}$$

Usually  $0 \le E_p \le 1$ , and is often written as a percentage

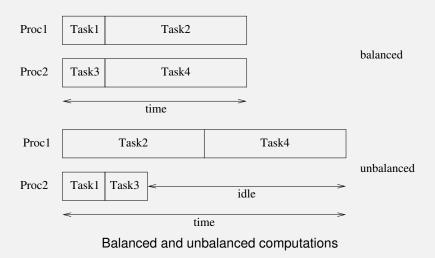

$E_p = 0.5$  (50%) means we are using only half of the processors' capabilities on our computation; half is lost in overheads or idling while waiting for something

$E_p = 1$  (100%) means we are using all the processors all the time on our computation

$E_p > 1$  indicate superlinear speedup: we are using more than 100% of the processors!

Efficiency is useful when we need to gauge the cost of a parallel system: the higher the efficiency the better the utilisation of the processors

When  $E_{\rho} < 1$  this indicates that somewhere at some point a processor not working on the computation. Perhaps it is occupied in communication; or possibly just lying idle waiting

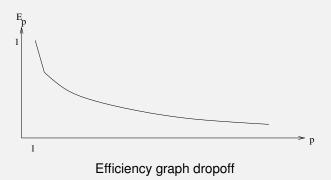

Typical efficiency graph on a fixed size problem:

#### Analysis Speedup and Efficiency

As an example of calculating speedup and efficiency we consider a pipeline (systolic array)

Systolic array

Data moves from one processor to the next being transformed at each stage: we assume one time step per transform

This could equally be a CPU instruction pipeline

#### Analysis Speedup and Efficiency

A *p*-stage pipeline will take *p* time steps to fill; after that it produces one result per time step

So it can produce *n* results in p + n - 1 time steps

A sequential system will take *np* time steps to do the *p* steps on the *n* computations

### Analysis Speedup and Efficiency

The speedup is

$$S_p = \frac{np}{p+n-1} = \frac{p}{(p-1)/n+1}$$

As time passes, the number of tasks *n* gets large, and  $S_p

ightarrow p$

A p-stage pipeline has a speedup is less than p, but that gets closer to p as time progresses

Also, the speedup starts low (for n = 1,  $S_p = p/(p+1-1) = 1$ ) and increases over time, getting closer and closer to p

### Analysis Speedup and Efficiency

The efficiency is

$$E_p = \frac{S_p}{p} = \frac{n}{p+n-1} = \frac{1}{(p-1)/n+1}$$

As *n* gets large,  $E_p \rightarrow 1$

Eventually we are (close to) using all the processors all the time: perfect efficiency!

Also, the efficiency starts low (for n = 1,  $E_p = 1/(p + 1 - 1) = 1/p$ ) and increases over time

#### Analysis Speedup and Efficiency

Pipelines are a really good way of making something parallel: both great speedup and great efficiency

As long as we can keep the pipeline full: in a CPU each time we take a jump the instruction pipeline breaks, empties and needs to refill

To keep high efficiency we need to avoid this: thus the complications in the designs of modern processors that are aimed at keeping the pipeline full

(Things like speculative evaluation and branch prediction, using many transistors...)

Speedup and Efficiency are simple, but useful measures of a parallel system, as long as you take care over using them

There are many other measures that are occasionally used, but they are of lesser importance

**Exercise** Some people use the phrase "negative speedup" rather than "slowdown". Why is that incorrect?

Sometimes people use the *Karp-Flatt metric* as a measure of an implementation to see how well it is doing

This is essentially an empirical measure of the sequential fraction of a computation (important for the Amdahl limit)

$$\mathbf{e} = \frac{\frac{1}{S_p} - \frac{1}{p}}{1 - \frac{1}{p}}$$

where  $S_p$  is the measured speedup and p the number of processors

### Analysis Karp-Flatt

A larger e indicates a larger sequential part

If we have perfect speedup,  $S_p = p$ , and e = 0

If we have no speedup,  $S_p = 1$ , and e = 1

If we have slowdown, e.g.,  $S_{p} = 1/2$ , and  $e \approx 2$

(If we have superlinear speedup,  $S_{\rho} > p$ , and e < 0)

**Exercise** Calculate Karp-Flatt for the pipeline. What does it tell us?

Note that Karp-Flatt will give you an estimate for the sequential time for a given implementation

It does not tell us the sequential limit for the problem

After all, you might just have a poor implementation

A big Karp-Flatt value is often an indication you need to re-think your code

Next: a parallel algorithm is *work efficient* (*cost efficient*) if the number of operations it performs is no more than the sequential algorithm

For example, a parallel algorithm might duplicate some operations on separate processors as it is more convenient, or reduces communications

The parallel overhead is

$$T_o = pT_p - T_s$$

where  $T_s$  is the sequential time and  $T_p$  is the parallel time

This measures the amount of extra work we are doing to get the parallelism

A measure of the extra energy expended in the parallel algorithm or implementation

And the cost of the overheads (e.g., communication) when we measure a real implementation

**Exercise** Calculate the parallel overhead for the pipeline. What does it tell us?

Another question is "how scalable is this algorithm?"

Here we ask for a relationship between p, the number of processors and n the size of the problem for a given efficiency

If we increase *p*, how much to we have to increase *n* to maintain a given efficiency?

Increasing *p* will generally decrease efficiency (Amdahl)

Increasing *n* will generally increase efficiency (Gustafson)

A poorly scalable algorithm will need to increase n a lot to maintain efficiency as we increase p

This relationship is called the *isoefficiency*, and expresses n as a function of p

It quantifies the balance between Amdahl and Gustafson

#### Analysis Isoefficiency

Computing the isoefficiency can be a bit fiddly, but often it is easiest to start by looking at the parallel overhead

We have efficiency  $E = T_s/pT_p$  and overhead  $T_o = pT_p - T_s$ . Combining these:

$$E = \frac{T_s}{p\left(\frac{T_o + T_s}{p}\right)} = \frac{T_s}{T_o + T_s} = \frac{1}{1 + T_o/T_s}$$

So to keep *E* constant, we need to keep  $T_o/T_s$  constant

So we must have

$$T_s = cT_o$$

for some constant *c*

As both  $T_s$  and  $T_o$  depend on *n* and *p*, this equation generally gives us enough to solve for *n* in terms of *p*

#### Analysis Isoefficiency

Example. The *p*-stage pipeline had efficiency

$$E=n/(p+n-1)$$

on a problem of size *n*

The overhead

$$T_o = pT_p - T_s = p(p+n-1) - np = p^2 - p$$

independent of *n*

This fixed overhead again tells us it is a good idea to keep the pipeline full!

#### Analysis Isoefficiency

We want  $T_s = cT_o$  which is

$$np = c(p^2 - p)$$

We solve for n

$$n=c(p-1)$$

Thus the isoefficiency is

n = O(p)

This is linear in p: if we double p we need only double n to maintain efficiency

So this tells us pipelines are very scalable

There are many ways we can measure if our parallel program is performing well, or poorly

But we do need to be careful that we are making meaningful comparisons of parallel and sequential algorithms

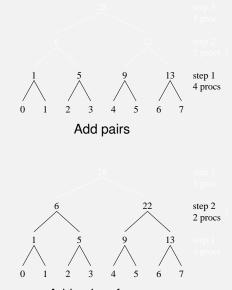

**Exercise** Compute these measures for summing *n* numbers using *p* processors

While we are thinking about measurement of parallel systems we need to make a quick comment about *bandwidth* and *latency* as they play an important role in the way we regard communications overhead

Bandwidth is the number of bytes per second transmitted over some medium

Latency is how long we have to wait for the data to arrive

Bandwidth is often mentioned in descriptions of things as it is easy to visualise (a rate of flow)

However, latency is often just as important in parallel systems